Infotainment systems can entertain passengers while helping drivers safely travel to their destinations, and this is no longer a patent for high-end vehicles: the emerging automotive driver assistance systems are now entering the mainstream market. The front liquid crystal display needs to be dynamically switched from the GPS display to one of many cameras, even a combination of images taken by several cameras around the vehicle. The image of the rear camera assists in parallel parking, ensuring that you leave the parking space and drive safely on the driveway and avoid collisions with oncoming vehicles. In order to expand the driver's view at the busy intersection, the front camera (two cameras mounted on the body above the two front wheels) can display images. Some vehicles are able to provide a "view of the surrounding image", which is basically a virtual 360-degree view of the body, from the front (the tip of the hood), the rear and the two sides (side mirrors) of the camera. For different sizes of LCD screens, these images may need to be scaled (sized), adjusted and enhanced to improve image quality.

This article refers to the address: http://

A new IC is required to manage image data. ASICs are expensive and risky, and ASSPs are not flexible. Programmable logic devices (PLDs) overcome these shortcomings, but they are faced with interface challenges for image data, which often require high performance and the cost of using programmable logic devices is high. However, this situation is changing. A new generation of low-cost programmable logic devices with high-performance IO buffers is now available. These low-cost programmable logic devices provide efficient transmission, processing, operation, and display of digital data while differentiated products, helping to achieve time-to-market and cost-effective targets.

Transfer image data

Various methods are used to transmit image data on the vehicle. A common approach is to use LVDS to establish a source synchronous interface.

A popular technology for video applications is the 7:1 LVDS (Low Voltage Differential Signaling) interface. Channel connections, camera connections, flat panel connections and FlatLink are variants of this approach. LVDS is a high speed, low power, universal interface standard. It uses a pair of differential signals that produce equal and opposite currents, which also helps to reduce total radiation. In addition, LVDS uses current mode drive, which limits power consumption. National Semiconductor has developed LVDS-based channel connectivity and FPD connectivity (panel display connectivity) technology as a flat panel display solution that supports data transfer from graphics controllers to LCD panels. The technology was later extended to a common data transfer method. The camera connection is a 7:1 LVDS based standard that uses up to 28 bits of data with a clock frequency of up to 85 Gpbs and a total throughput of 2.38 MHz. Texas Instruments' FlatLink offers 21:3 or 28:4 configurations with support for 4-bit, 6-bit or 8-bit RGB.

LVDS7:1 with low-cost programmable logic device challenges

The 7:1 LVDS interface typically uses three to five LVDS data channels and one LVDS clock channel. Higher resolution displays use four or five LVDS data channels. There are 7 serial bits in each data channel in one clock cycle or cycle, as shown in Figure 1.

Figure 1 7: 1 Timing of the LVDS interface

The 7:1 challenge of implementing LVDS interfaces with low-cost programmable logic devices includes high-speed LVDS buffers and PLLs for generating deserialized clocks that capture input data with efficient, accurate matching and data formatting.

High Speed ​​LVDS Buffer: Must be able to receive or transmit data and clocks to or from programmable logic devices at relatively high speeds. The exact speed depends on the resolution, frame rate, and color depth used by the display. For example, for a refresh rate of 60 Hz to 75 Hz, a display of 800 x 600 to 1024 x 768 requires LVDS data transmission from 40 MHz to 78.5 MHz. This translates to LVDS data rates from 280Mbps to 549Mbps. Higher resolution displays, such as 1280 x 1024, 60 Hz, require data to be transmitted with a 108 MHz clock. For these systems, data is transmitted at 756 Mbps.

Clock Generator: The usual method is to receive the input clock and use a phase-locked loop that is 7 times the clock frequency for each data bit. In fact, this is quite difficult because the clock runs extremely fast. Since the typical display interface clock rate is 60MHz~100MHz or higher, multiplying by 7 produces a frequency of 420MHz to 700MHz. Operating at these clock rates, any image control and processing is not possible with a low cost PLD.

Data Acquisition, Matching, and Formatting: Registers that follow the LVDS input buffer must accurately capture the data. Strict control of clock and data relationships is important to capture the high-speed data streams that are sent. It is also necessary to match (reduce) the speed of the data passed to the PLD. If the input capture circuit only runs on the edge of one clock, the phase shift of the seven low-speed clocks should be generated and the input data captured with seven different registers. The challenges of clock generation and distribution hinder the implementation of PLDs. The clock must have relatively low jitter because its jitter must be calculated throughout the timing budget. Also, in any timing analysis, the offset of the clock distribution network used to provide the clock input or output registers must be considered. Implementing an 7:1 LVDS instance in a MachXO2 device

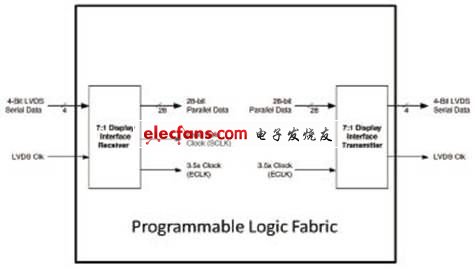

The programmable logic device MachXO2 has a specific functional architecture supporting a 7:1 LVDS interface. These features include high-performance LVDS I/O buffers, dual data rate (DDR) I/O registers, matching logic, and high-precision phase-locked loops with dedicated 3.5-clock dividers. These features and functions provide a complete solution. MachXO2 devices offer up to 21 data channels. Figure 2 shows the four data channels of the receiver and transmitter.

Figure 2 Receiver and Transmitter in MachXO2

In this figure, the receive module of the MachXO2 device receives four data channels and the clock through the LVDS I/O buffer. These buffers can run up to 303 MHz (606 Mbps), support high resolution, and display refresh rates up to 85 MHz pixel rate (SXGA). The PLL is multiplied by 3.5 clock. The faster phase shift clock (ECLK) is then distributed through a clock network with a low offset edge to the DDR capture register. The LVDS data is fed into a DDR register with a 7:1 match. This match demultiplexes the I/O data with the high speed EDGE clock (ECLK) and then to the slower FPGA clock frequency (SCLK).

This 7:1 LVDS solution includes automatically aligning the PLL output clock to the optimal position for sampling the input LVDS data stream, adding logic to automatically align the programmable logic device's clock to input data words. These "soft" logics echo the "hard" resources to provide a complete display interface solution.

The transmit module of the MachXO2 PLD receives 28 bits of parallel data and a fast DDR clock (ECLK). Parallel data is fed into the display I/O logic unit with 7:1 matching. The matching function multiplexes input data with a low speed system clock (SCLK) to a higher speed DDR output edge clock rate (ECLK).

to sum up

With many image sources (several cameras) to add digital content, rear-seat displays and navigation systems are entering the mainstream market.

In terms of image applications, the 7:1 LVS interface is expected to remain popular due to cost and power consumption, such as in-vehicle infotainment systems.

MachXO2 devices can be deployed in automotive driver assistance systems to manage the display and operation (zoom, rotate, etc.) of images from the camera. MachXO2 devices can dynamically switch between one camera and other camera display images, or combine the two.

Multi-core cpu is more and more popular, people are used to take dual core processors laptop before. However, Quad Core Laptop is becoming selling like a hot cake nowadays. You can find Quad Core Processor Laptop at our store, like I3 Quad Core Laptop,I7 Quad Core Laptop, I5 Quad Core Laptop, intel celeron J4125 or N5095 15.6 Inch Laptop, even N4120 quad core 14 Inch Laptop, etc. Therefore, you can just share the parameters prefer, like size, cpu, ram, rom, gpu, application scenarios, thus save much time to get a win-win solution.

Do you know the reason why more people choose quad core device? The core reason is that heavier tasks people need to finish at a higher speed than before. Nowadays quick rhythm is becoming the main style in city even everyone is eager to downshifting. So more powerful laptop, computer, mobile phone is a trend, though most functions never are used in lifetime.

Other 15.6 inch Gaming Laptop or 14 Inch Gaming Laptop is becoming the most popular level at the market.

Quad Core Laptop,I3 Quad Core Laptop,I7 Quad Core Laptop,I5 Quad Core Laptop,Quad Core Processor Laptop

Henan Shuyi Electronics Co., Ltd. , https://www.shuyiaiopc.com