This paper introduces the abnormal interrupt mechanism of ARM S3C4510B system, including classification of abnormal interrupt, response and return; installation and invocation of interrupt handler; SWI, instance and key code of IRQ interrupt.

As people's requirements for electronic products are getting higher and higher, 8-bit processor systems represented by the 80C51 series are beginning to face more and more limitations and challenges. People are increasingly calling for high-performance chips and embedded functions. high. The 16/32-bit processor system has received unprecedented attention and attention. The 32-bit ARM system series processor is one of them. The S3C4510B processor is based on the ARM7 system 16/32-bit RISC processor. It integrates 8KB of CACHE/SDRAM, embedded EARTHNET controller, and has 7 processor modes and internal multi-thread and external multi-processor processor architecture. The abort technology, which is of great significance in embedded systems, also embodies some unique features of the ARM system in the S3C4510B system. According to the characteristics of S3C4510B system, this paper analyzes the functions and characteristics of seven kinds of abnormal interruptions in this system. The application example code of SWI abnormal interrupt (external interrupt) and IRQ abnormal interrupt (software interrupt) is given.

1 Abnormal interruption in the S3C4510B system

1.1 Characteristics of S3C4510B System Abnormal Interruption

There are usually three ways to control the execution flow of the program in the S3C4510B system. One is the normal program execution process, that is, the program counter PC is added according to the instruction type to make the program execute sequentially. The second is to control the execution of the program by jumping. The command execution jump operation can also achieve the purpose of jump by directly modifying the program counter; the third is the way of abnormal interrupt, which can realize internal and external exception processing according to the execution of the software, the abnormal request of the external device, etc. Functions such as function calls and program process control.

The abnormal interruption of the S3C4510B system has the following characteristics. First of all, as part of the ARM system RTOS (real-time operating system), the abnormal interrupt in the program must be converted according to the requirements of the ARM system. Secondly, if there is a need for system optimization, 32-bit ARM processing instructions and 16-bit THUMB instructions can be converted. In addition, when the S3C4510B processor is running normally, the saved return address is completed by storing the PC in the LR register. The value of the counter PC is sometimes updated due to the interrupt generation, such as external interrupts and fast interrupts; sometimes it may not be Updates, such as software interrupts and undefined instruction aborts, etc., so the return address must be modified according to the actual situation before it can be returned correctly. Finally, note that the ARM architecture supports calls between C and assembly language programs and is coordinated by ATPCS rules, so the exception handler must perform register processing in accordance with the ATPCS rules.

1.2 Types of Abnormal Interrupts in the S3C4510B System

The S3C4510B has seven different types of abort that are adapted to different interrupt needs. According to the characteristics of the ARM series processor, various abnormal interrupts correspond to different working modes of the ARM series. The types and corresponding relationships are shown in Table 1.

Among them, the reset interrupt is the highest priority interrupt. On the premise that the reset pin is valid, the system will cause a reset interrupt when the system is powered up or reset. Data access abort occurs when the destination address of the data access instruction does not exist or the address does not allow access by the current instruction. The instruction prefetch abort interrupt is that the processor or system coprocessor considers that the current instruction is undefined. When the system prefetches the instruction, the interrupt is executed. The undefined abort is generated when the processor or system coprocessor considers that the current instruction is undefined, so the floating point vector operation can be simulated according to the abnormal interrupt mechanism. Both the fast interrupt and the external interrupt are generated when the corresponding interrupt request pin is valid and the corresponding interrupt disable flag in the status register is cleared. The external interrupt can also be used to switch between various system processes; the soft interrupt is defined by the user, and is called by the SWI instruction when the program is running, and can be used for the program in the user mode to invoke the privileged mode instruction. System function calls can be implemented in the RTOS system through this interrupt mechanism.

1.3 S3C4510B System Response to Abnormal Interruption

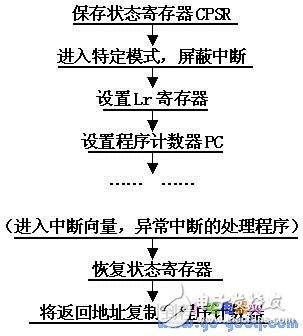

The response process of the S3C4510B system to the abnormal interrupt is as follows:

(1) Save the value of the processor current status register CPSR, interrupt mask, and each condition flag to the SPSR of the abort to be executed. Electronic circuit diagram

(2) Set the value of the current program status register CPSR. These include setting the value of the corresponding bit of the CPSR to put the processor into a specific processor mode; masking the interrupt as required, usually masking the IRQ interrupt, shielding the FIQ interrupt during the FIQ interrupt.

(3) Set the Lr register. Set the value of the Lr register that interrupts the corresponding mode to the return address of the abort.

(4) Processing program counter PC. The PC value is set to the address of the corresponding interrupt vector, thereby implementing a jump to execute the interrupt routine.

Socket Connector,Board-To-Board Socket Connectors,Horizontal Socket Connector,Screw Male Socket Connector

Shenzhen Jinyicheng Electronci Technology Co.,Ltd. , https://www.jycconnector.com