From the core of the network to the edge devices, a major transformation is taking place. The wireless market is witnessing millions of "always on" connections, while next-generation backhaul communications are facing unprecedented data transmission demands. At the same time, existing wired infrastructure is being pushed to support a wide range of broadband consumer applications. These factors are driving the evolution of modern networks, leading to significant upgrades across all layers.

As network operators aim to increase capacity without significantly raising costs, it’s often impractical to replace all existing hardware. Factors such as product launch timelines, upgrade expenses, and software compatibility must be carefully considered. When upgrading equipment, it's essential to provide necessary "refurbishment" to extend device lifespans and add features that meet future network needs. Many network equipment providers (NEPs) have found that mid-range FPGAs with transceiver capabilities offer an effective solution for these challenges.

Mid-range FPGAs represent a new class of devices designed with cost and power efficiency in mind. They combine the flexibility of traditional FPGAs with advanced features typically found in high-end models. For instance, they offer optimized serial interfaces (SERDES) that bridge the gap between current and next-gen communication solutions. These FPGAs can be configured to support various data rates and interface standards—whether industry-standard or proprietary. Moreover, the number of SERDES channels varies per model, allowing designers to tailor their solutions for specific performance, cost, and power goals.

The configurability of serial interfaces in mid-range FPGAs gives them a unique competitive edge. While some vendors once relied on custom interface designs, today’s market demands interoperability between devices from different suppliers. Implementing standard serial interfaces not only speeds up system design but also enhances compatibility, reliability, and vendor reach. This trend is pushing large system vendors to offer complete solutions, while others seek differentiated options that fit into industry-standard chassis or operate as standalone “thin devices.â€

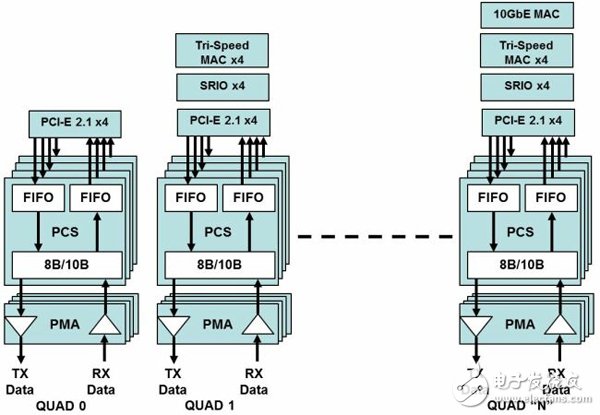

A key feature of implementing serial interfaces is the ability to create scalable data links that match bandwidth requirements. Mid-range FPGAs integrate hardened PMA and PCS logic blocks, which work together to support multiple protocols. This allows for flexible configuration where one protocol can use several transceiver channels, while others remain available or disabled, reducing power consumption. Although the transceiver provides a physical layer interface through PMA and PCS blocks, higher-level logic is still needed to build a full industry-standard solution. While application-specific standard products (ASSPs) may offer fixed interface solutions, they lack the flexibility required for diverse network access environments.

High-end FPGAs based on SERDES can include extensive serial logic, but at the cost of increased design complexity, power usage, and size. Mid-range FPGAs, however, offer another advantage for board and system designers. By integrating a certain number of transceivers along with hardened transport protocol logic, they provide a flexible, low-cost, and compact communication solution. As shown in Figure 1, different transport protocols can be easily implemented by selecting the right FPGA model.

Figure 1: Mid-range FPGA with transceiver capability

The access network includes infrastructure from various operators, and many legacy devices will continue to be used for years. As a result, more operators are moving toward all-packet networks. With this shift, standard technologies like Ethernet are becoming the dominant platform for control and data transmission. Ethernet’s long history, widespread adoption, and support for IP packets make it a natural choice for next-gen networks. Similarly, PCI-Express is widely used in computing, servers, and consumer electronics, serving as a backbone for device-level and backplane interconnects. It’s also replacing parallel PCI buses in many applications. Meanwhile, the Serial Wireless IO standard is used in wireless, DSP, and embedded systems. Many mid-range FPGAs support these key standards, offering manufacturers a rich set of hardened solutions. Beyond cost and power advantages, these devices eliminate the need to implement and verify communication protocols, allowing designers to focus on building their own differentiated solutions and system upgrades within the FPGA fabric.

3.2v12-30Ah Lithium Battery Cells

3.2v12-30Ah Lithium Battery Cells,3.2v12-30Ah Lithium Battery Cells price,3.2v12-30Ah Lithium Battery Cells product

Jiangsu Zhitai New Energy Technology Co.,Ltd , https://www.zttall.com